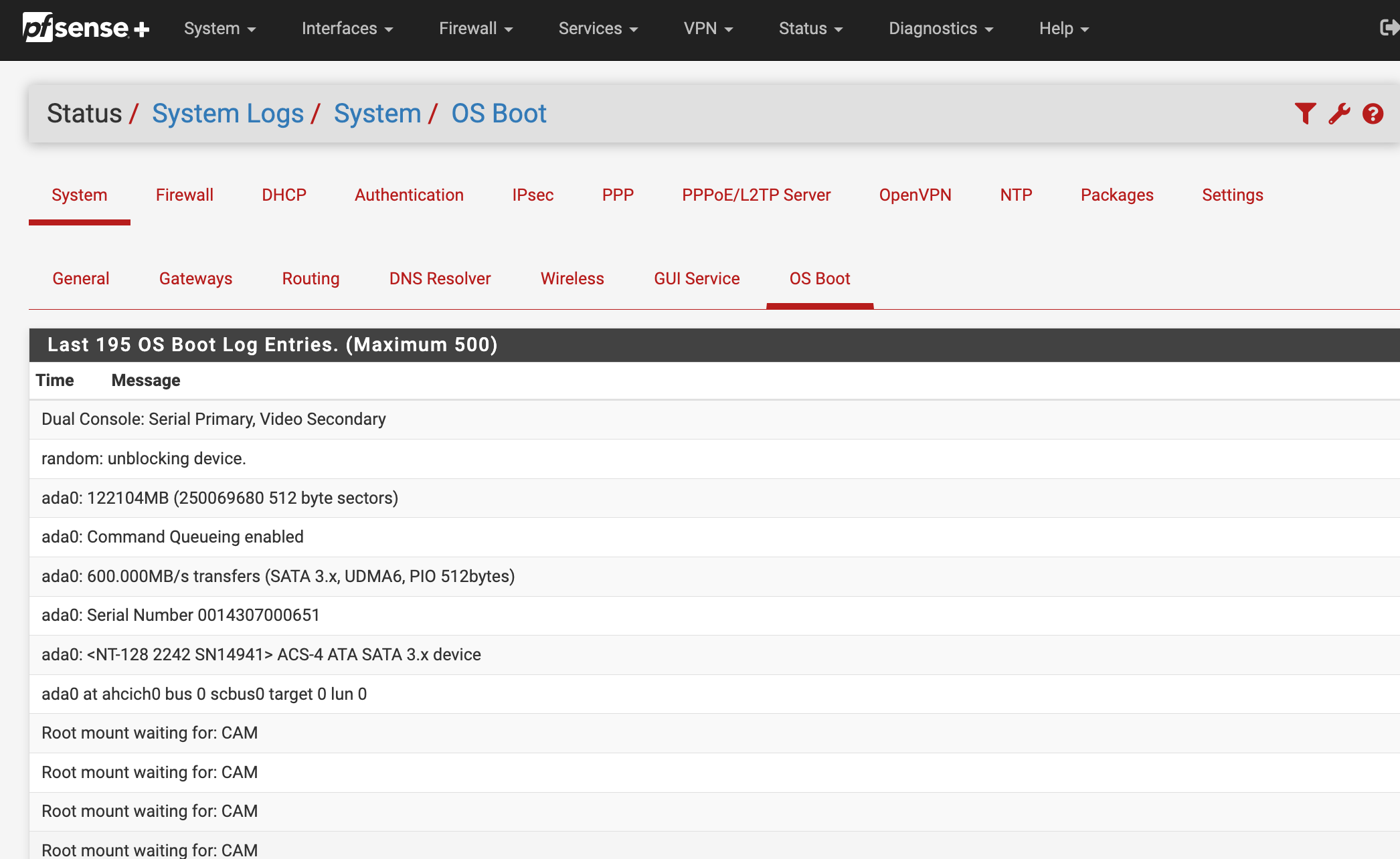

Resolved: 23.09.01 Boot Loader logs hang at Dual Console: Serial Primary, Video Secondary

-

It normally displays this at the end after 23.09.01 upgrade it just hangs in logs

-

S stephenw10 moved this topic from Problems Installing or Upgrading pfSense Software on

S stephenw10 moved this topic from Problems Installing or Upgrading pfSense Software on

-

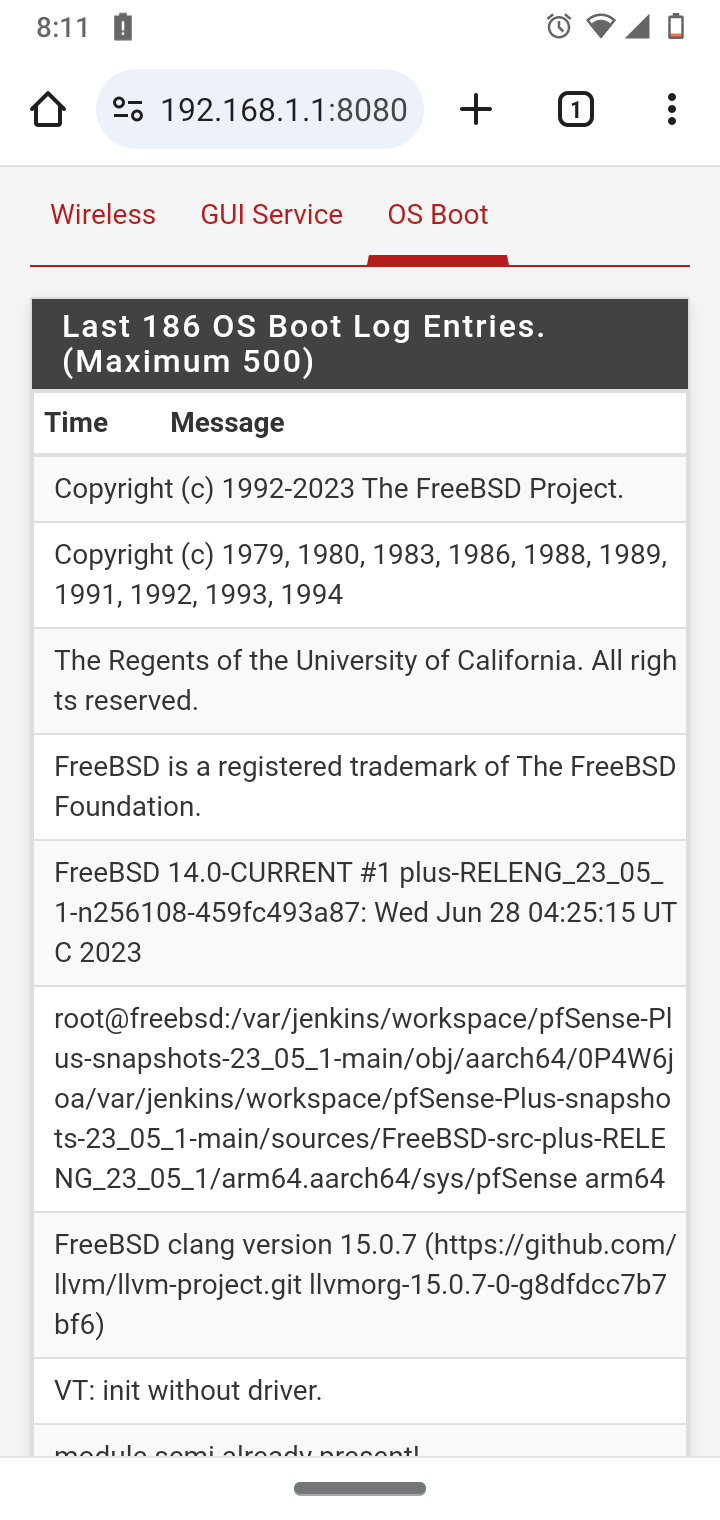

This is it in 23.05.01

-

That's the beginning of the boot log in 23.05.1 with the FreeBSD copyright info etc.

Later in the boot it repeats a lot of the CPU info when it loads them as devices. The only thing that has changed there is it shows the console setting last.

23.05.1 boot log:

Copyright (c) 1992-2023 The FreeBSD Project. Copyright (c) 1979, 1980, 1983, 1986, 1988, 1989, 1991, 1992, 1993, 1994 The Regents of the University of California. All rights reserved. FreeBSD is a registered trademark of The FreeBSD Foundation. FreeBSD 14.0-CURRENT #1 plus-RELENG_23_05_1-n256108-459fc493a87: Wed Jun 28 04:25:15 UTC 2023 root@freebsd:/var/jenkins/workspace/pfSense-Plus-snapshots-23_05_1-main/obj/aarch64/0P4W6joa/var/jenkins/workspace/pfSense-Plus-snapshots-23_05_1-main/sources/FreeBSD-src-plus-RELENG_23_05_1/arm64.aarch64/sys/pfSense arm64 FreeBSD clang version 15.0.7 (https://github.com/llvm/llvm-project.git llvmorg-15.0.7-0-g8dfdcc7b7bf6) VT: init without driver. module scmi already present! module firmware already present! real memory = 3602866176 (3435 MB) avail memory = 3462991872 (3302 MB) Starting CPU 1 (1) FreeBSD/SMP: Multiprocessor System Detected: 2 CPUs arc4random: WARNING: initial seeding bypassed the cryptographic random device because it was not yet seeded and the knob 'bypass_before_seeding' was enabled. random: entropy device external interface ipw_bss: You need to read the LICENSE file in /usr/share/doc/legal/intel_ipw.LICENSE. ipw_bss: If you agree with the license, set legal.intel_ipw.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (ipw_bss_fw, 0xffff000000252de4, 0) error 1 ipw_ibss: You need to read the LICENSE file in /usr/share/doc/legal/intel_ipw.LICENSE. ipw_ibss: If you agree with the license, set legal.intel_ipw.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (ipw_ibss_fw, 0xffff000000252e90, 0) error 1 ipw_monitor: You need to read the LICENSE file in /usr/share/doc/legal/intel_ipw.LICENSE. ipw_monitor: If you agree with the license, set legal.intel_ipw.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (ipw_monitor_fw, 0xffff000000252f3c, 0) error 1 iwi_bss: You need to read the LICENSE file in /usr/share/doc/legal/intel_iwi.LICENSE. iwi_bss: If you agree with the license, set legal.intel_iwi.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (iwi_bss_fw, 0xffff000000252fe8, 0) error 1 wlan: mac acl policy registered iwi_ibss: You need to read the LICENSE file in /usr/share/doc/legal/intel_iwi.LICENSE. iwi_ibss: If you agree with the license, set legal.intel_iwi.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (iwi_ibss_fw, 0xffff000000253094, 0) error 1 iwi_monitor: You need to read the LICENSE file in /usr/share/doc/legal/intel_iwi.LICENSE. iwi_monitor: If you agree with the license, set legal.intel_iwi.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (iwi_monitor_fw, 0xffff000000253140, 0) error 1 MAP 8000000 mode 2 pages 5 MAP 7ffc6000 mode 2 pages 1 MAP e7ff6000 mode 2 pages 1 kbd0 at kbdmux0 ofwbus0: <Open Firmware Device Tree> simplebus0: <Flattened device tree simple bus> on ofwbus0 simplebus1: <Flattened device tree simple bus> on simplebus0 simple_mfd0: <Simple MFD (Multi-Functions Device)> mem 0x13800-0x138ff,0x13c00-0x13c1f on simplebus1 simple_mfd1: <Simple MFD (Multi-Functions Device)> mem 0x18800-0x188ff,0x18c00-0x18c1f on simplebus1 psci0: <ARM Power State Co-ordination Interface Driver> on ofwbus0 netgate0: <Netgate 2100> gic0: <ARM Generic Interrupt Controller v3.0> mem 0x1d00000-0x1d0ffff,0x1d40000-0x1d7ffff,0x1d80000-0x1d81fff,0x1d90000-0x1d91fff,0x1da0000-0x1dbffff irq 27 on simplebus1 gpio0: <Armada 37x0 North Bridge GPIO Controller> mem 0x13800-0x138ff,0x13c00-0x13c1f irq 28,29,30,31,32,33,34,35,36,37,38,39 on simple_mfd0 gpiobus0: <OFW GPIO bus> on gpio0 gpio1: <Armada 37x0 South Bridge GPIO Controller> mem 0x18800-0x188ff,0x18c00-0x18c1f irq 40,41,42,43,44 on simple_mfd1 gpiobus1: <OFW GPIO bus> on gpio1 gpiomdio0: <GPIO MDIO bit-banging Bus driver> at pins 21,23 on gpiobus1 gpiomdio0: MDC pin: 21, MDIO pin: 23 a37x0-xtal0: <Marvell Armada 3700 Oscillator> mem 0x13800-0x138ff,0x13c00-0x13c1f on simple_mfd0 generic_timer0: <ARMv8 Generic Timer> irq 0,1,2,3 on ofwbus0 Timecounter "ARM MPCore Timecounter" frequency 12500000 Hz quality 1000 Event timer "ARM MPCore Eventtimer" frequency 12500000 Hz quality 1000 a37x0_tbg0: <Marvell Armada 3700 time base generators> mem 0x13200-0x132ff on simplebus1 a37x0_nb_periph_driver0: <marvell,armada-3700-nb-periph-clock> mem 0x13000-0x130ff on simplebus1 a37x0_sb_periph_driver0: <marvell,armada-3700-sb-periph-clock> mem 0x18000-0x180ff on simplebus1 cpulist0: <Open Firmware CPU Group> on ofwbus0 cpu0: <Open Firmware CPU> on cpulist0 cpu1: <Open Firmware CPU> on cpulist0 pmu0: <Performance Monitoring Unit> irq 4 on ofwbus0 spi0: <Armada 37x0 SPI controller> mem 0x10600-0x10fff irq 6 on simplebus1 iichb0: <Marvell Armada 37x0 IIC controller> mem 0x11000-0x11023 irq 7 on simplebus1 iicbus0: <OFW I2C bus> on iichb0 iic0: <I2C generic I/O> on iicbus0 iichb1: <Marvell Armada 37x0 IIC controller> mem 0x11080-0x110a3 irq 8 on simplebus1 iicbus1: <OFW I2C bus> on iichb1 iic1: <I2C generic I/O> on iicbus1 nxprtc0: <NXP PCF8563 RTC> at addr 0xa2 on iicbus1 gpio2: <ISSI IS31FL3199 9 channel light effect LED driver> at addr 0xce on iicbus1 gpiobus2: <OFW GPIO bus> on gpio2 gpioc2: <GPIO controller> on gpio2 uart0: <Marvell Armada 3700 UART> mem 0x12000-0x121ff irq 9,10,11 on simplebus1 uart0: console (115200,n,8,1) gpioc0: <GPIO controller> on gpio0 gpioc1: <GPIO controller> on gpio1 mvneta0: <NETA controller> mem 0x30000-0x33fff irq 14 on simplebus1 mvneta0: version is 10 miibus0: <MII bus> on gpiomdio0 mv88e151x0: <Marvell 88E1512 Gigabit PHY> PHY 1 on miibus0 mv88e151x0: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, 1000baseSX, 1000baseSX-FDX, auto mvneta0: Ethernet address: 00:e0:ed:b6:13:59 mvneta1: <NETA controller> mem 0x40000-0x43fff irq 15 on simplebus1 mvneta1: version is 10 mdio0: <MDIO> on mvneta1 mdioproxy0: <MII/MDIO proxy, MDIO side> on mdio0 e6000sw0: <Marvell 88E6141> on mdio0 e6000sw0: single-chip addressing mode e6000sw0: PHY at port 1 miibus1: <MII bus> on e6000sw0 e1000phy0: <Marvell 88E1000 Gigabit PHY> PHY 17 on miibus1 e1000phy0: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, auto e6000sw0: PHY at port 2 miibus2: <MII bus> on e6000sw0 e1000phy1: <Marvell 88E1000 Gigabit PHY> PHY 18 on miibus2 e1000phy1: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, auto e6000sw0: PHY at port 3 miibus3: <MII bus> on e6000sw0 e1000phy2: <Marvell 88E1000 Gigabit PHY> PHY 19 on miibus3 e1000phy2: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, auto e6000sw0: PHY at port 4 miibus4: <MII bus> on e6000sw0 e1000phy3: <Marvell 88E1000 Gigabit PHY> PHY 20 on miibus4 e1000phy3: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, auto e6000sw0: CPU port at 5 e6000sw0: fixed port at 5 e6000sw0: switch is ready. etherswitch0: <Switch controller> on e6000sw0 mvneta1: Ethernet address: 00:e0:ed:b6:13:5a xhci0: <Generic USB 3.0 controller> mem 0x58000-0x5bfff irq 16 on simplebus1 xhci0: 32 bytes context size, 32-bit DMA usbus0 on xhci0 ehci0: <Marvell Integrated USB 2.0 controller> mem 0x5e000-0x5ffff irq 17 on simplebus1 usbus1: EHCI version 1.0 usbus1 on ehci0 sdhci_xenon0: <Armada Xenon SDHCI controller> mem 0xd8000-0xd82ff,0x17808-0x1780b irq 25 on simplebus1 mmc0: <MMC/SD bus> on sdhci_xenon0 ahci0: <AHCI SATA controller> mem 0xe0000-0xe1fff irq 26 on simplebus1 ahci0: AHCI v1.30 with 1 6Gbps ports, Port Multiplier supported with FBS ahcich0: <AHCI channel> at channel 0 on ahci0 pcib0: <Marvell Armada 3700 PCIe Bus Controller> mem 0xd0070000-0xd008ffff irq 5 on simplebus0 pcib0: link up pci0: <OFW PCI bus> on pcib0 ath0: <Atheros 9280> at device 0.0 on pci0 [ath] enabling AN_TOP2_FIXUP ath0: [HT] enabling HT modes ath0: [HT] 1 stream STBC receive enabled ath0: [HT] 1 stream STBC transmit enabled ath0: [HT] 2 RX streams; 2 TX streams ath0: AR9280 mac 128.2 RF5133 phy 13.0 ath0: 2GHz radio: 0x0000; 5GHz radio: 0x00c0 armv8crypto0: <AES-CBC,AES-XTS,AES-GCM> Timecounters tick every 1.000 msec mvneta1: link state changed to UP ZFS filesystem version: 5 ZFS storage pool version: features support (5000) usbus0: 5.0Gbps Super Speed USB v3.0 usbus1: 480Mbps High Speed USB v2.0 [nl_generic_kpi] genl_register_family: Registered family nlctrl id 16 [nl_generic_kpi] genl_register_cmds: Adding cmd GETFAMILY(3) to family nlctrl ugen0.1: <Generic XHCI root HUB> at usbus0 uhub0 on usbus0 uhub0: <Generic XHCI root HUB, class 9/0, rev 3.00/1.00, addr 1> on usbus0 ugen1.1: <Marvell EHCI root HUB> at usbus1 uhub1 on usbus1 uhub1: <Marvell EHCI root HUB, class 9/0, rev 2.00/1.00, addr 1> on usbus1 [nl_generic_kpi] genl_register_family: Registered family carp id 17 [nl_generic_kpi] genl_register_cmds: Adding cmd SIOCGVH(1) to family carp [nl_generic_kpi] genl_register_cmds: Adding cmd SIOCSVH(2) to family carp spibus0: <OFW SPI bus> on spi0 mx25l0: <M25Pxx Flash Family> at cs 0 mode 0 on spibus0 mx25l0: device type w25q32, size 4096K in 64 sectors of 64K, erase size 4K nxprtc0: registered as a time-of-day clock, resolution 0.015625s mmc0: Failed to set VCCQ for card at relative address 2 mmcsd0: 8GB <MMCHC DG4008 0.1 SN A401600F MFG 09/2019 by 69 0x0000> at mmc0 50.0MHz/8bit/65535-block mmcsd0boot0: 4MB partition 1 at mmcsd0 mmcsd0boot1: 4MB partition 2 at mmcsd0 mmcsd0rpmb: 4MB partition 3 at mmcsd0 CPU 0: ARM Cortex-A53 r0p4 affinity: 0 Cache Type = <64 byte D-cacheline,64 byte I-cacheline,VIPT ICache,64 byte ERG,64 byte CWG> Instruction Set Attributes 0 = <CRC32,SHA2,SHA1,AES+PMULL> Instruction Set Attributes 1 = <> Instruction Set Attributes 2 = <> Processor Features 0 = <GIC,AdvSIMD,FP,EL3 32,EL2 32,EL1 32,EL0 32> Processor Features 1 = <> Memory Model Features 0 = <TGran4,TGran64,SNSMem,BigEnd,16bit ASID,1TB PA> Memory Model Features 1 = <8bit VMID> Memory Model Features 2 = <32bit CCIDX,48bit VA> Debug Features 0 = <DoubleLock,2 CTX BKPTs,4 Watchpoints,6 Breakpoints,PMUv3,Debugv8> Debug Features 1 = <> Auxiliary Features 0 = <> Auxiliary Features 1 = <> AArch32 Instruction Set Attributes 5 = <CRC32,SHA2,SHA1,AES+VMULL,SEVL> AArch32 Media and VFP Features 0 = <FPRound,FPSqrt,FPDivide,DP VFPv3+v4,SP VFPv3+v4,AdvSIMD> AArch32 Media and VFP Features 1 = <SIMDFMAC,FPHP DP Conv,SIMDHP SP Conv,SIMDSP,SIMDInt,SIMDLS,FPDNaN,FPFtZ> CPU 1: ARM Cortex-A53 r0p4 affinity: 1 Release APs...Trying to mount root from zfs:pfSense/ROOT/auto-default-20231207213047 []... done TCP_ratelimit: Is now initialized uhub0: 2 ports with 2 removable, self powered e6000sw0port1: link state changed to DOWN e6000sw0port2: link state changed to DOWN e6000sw0port3: link state changed to DOWN e6000sw0port4: link state changed to DOWN uhub1: 1 port with 1 removable, self powered ugen0.2: <Sierra Wireless, Incorporated EM7305> at usbus0 u3g0 on uhub0 u3g0: <Sierra Wireless, Incorporated EM7305, class 0/0, rev 2.00/0.06, addr 1> on usbus0 u3g0: Found 4 ports. Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM random: unblocking device.23.09.1 boot log:

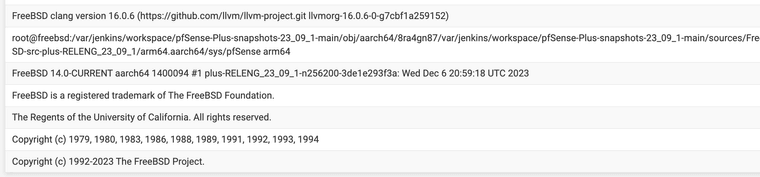

Copyright (c) 1992-2023 The FreeBSD Project. Copyright (c) 1979, 1980, 1983, 1986, 1988, 1989, 1991, 1992, 1993, 1994 The Regents of the University of California. All rights reserved. FreeBSD is a registered trademark of The FreeBSD Foundation. FreeBSD 14.0-CURRENT aarch64 1400094 #1 plus-RELENG_23_09_1-n256200-3de1e293f3a: Wed Dec 6 20:59:18 UTC 2023 root@freebsd:/var/jenkins/workspace/pfSense-Plus-snapshots-23_09_1-main/obj/aarch64/8ra4gn87/var/jenkins/workspace/pfSense-Plus-snapshots-23_09_1-main/sources/FreeBSD-src-plus-RELENG_23_09_1/arm64.aarch64/sys/pfSense arm64 FreeBSD clang version 16.0.6 (https://github.com/llvm/llvm-project.git llvmorg-16.0.6-0-g7cbf1a259152) VT: init without driver. module scmi already present! real memory = 3602866176 (3435 MB) avail memory = 3463016448 (3302 MB) Starting CPU 1 (1) FreeBSD/SMP: Multiprocessor System Detected: 2 CPUs arc4random: WARNING: initial seeding bypassed the cryptographic random device because it was not yet seeded and the knob 'bypass_before_seeding' was enabled. random: entropy device external interface ipw_bss: You need to read the LICENSE file in /usr/share/doc/legal/intel_ipw.LICENSE. ipw_bss: If you agree with the license, set legal.intel_ipw.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (ipw_bss_fw, 0xffff000000251810, 0) error 1 ipw_ibss: You need to read the LICENSE file in /usr/share/doc/legal/intel_ipw.LICENSE. ipw_ibss: If you agree with the license, set legal.intel_ipw.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (ipw_ibss_fw, 0xffff0000002518bc, 0) error 1 ipw_monitor: You need to read the LICENSE file in /usr/share/doc/legal/intel_ipw.LICENSE. ipw_monitor: If you agree with the license, set legal.intel_ipw.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (ipw_monitor_fw, 0xffff000000251968, 0) error 1 iwi_bss: You need to read the LICENSE file in /usr/share/doc/legal/intel_iwi.LICENSE. iwi_bss: If you agree with the license, set legal.intel_iwi.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (iwi_bss_fw, 0xffff000000251a14, 0) error 1 iwi_ibss: You need to read the LICENSE file in /usr/share/doc/legal/intel_iwi.LICENSE. iwi_ibss: If you agree with the license, set legal.intel_iwi.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (iwi_ibss_fw, 0xffff000000251ac0, 0) error 1 wlan: mac acl policy registered iwi_monitor: You need to read the LICENSE file in /usr/share/doc/legal/intel_iwi.LICENSE. iwi_monitor: If you agree with the license, set legal.intel_iwi.license_ack=1 in /boot/loader.conf. module_register_init: MOD_LOAD (iwi_monitor_fw, 0xffff000000251b6c, 0) error 1 kbd0 at kbdmux0 ofwbus0: <Open Firmware Device Tree> simplebus0: <Flattened device tree simple bus> on ofwbus0 simplebus1: <Flattened device tree simple bus> on simplebus0 simple_mfd0: <Simple MFD (Multi-Functions Device)> mem 0x13800-0x138ff,0x13c00-0x13c1f on simplebus1 simple_mfd1: <Simple MFD (Multi-Functions Device)> mem 0x18800-0x188ff,0x18c00-0x18c1f on simplebus1 psci0: <ARM Power State Co-ordination Interface Driver> on ofwbus0 netgate0: <Netgate 2100> gic0: <ARM Generic Interrupt Controller v3.0> mem 0x1d00000-0x1d0ffff,0x1d40000-0x1d7ffff,0x1d80000-0x1d81fff,0x1d90000-0x1d91fff,0x1da0000-0x1dbffff irq 27 on simplebus1 gpio0: <Armada 37x0 North Bridge GPIO Controller> mem 0x13800-0x138ff,0x13c00-0x13c1f irq 28,29,30,31,32,33,34,35,36,37,38,39 on simple_mfd0 gpiobus0: <OFW GPIO bus> on gpio0 gpio1: <Armada 37x0 South Bridge GPIO Controller> mem 0x18800-0x188ff,0x18c00-0x18c1f irq 40,41,42,43,44 on simple_mfd1 gpiobus1: <OFW GPIO bus> on gpio1 gpiomdio0: <GPIO MDIO bit-banging Bus driver> at pins 21,23 on gpiobus1 gpiomdio0: MDC pin: 21, MDIO pin: 23 a37x0-xtal0: <Marvell Armada 3700 Oscillator> mem 0x13800-0x138ff,0x13c00-0x13c1f on simple_mfd0 generic_timer0: <ARMv8 Generic Timer> irq 0,1,2,3 on ofwbus0 Timecounter "ARM MPCore Timecounter" frequency 12500000 Hz quality 1000 Event timer "ARM MPCore Eventtimer" frequency 12500000 Hz quality 1000 a37x0_tbg0: <Marvell Armada 3700 time base generators> mem 0x13200-0x132ff on simplebus1 a37x0_nb_periph_driver0: <marvell,armada-3700-nb-periph-clock> mem 0x13000-0x130ff on simplebus1 a37x0_sb_periph_driver0: <marvell,armada-3700-sb-periph-clock> mem 0x18000-0x180ff on simplebus1 cpulist0: <Open Firmware CPU Group> on ofwbus0 cpu0: <Open Firmware CPU> on cpulist0 pmu0: <Performance Monitoring Unit> irq 4 on ofwbus0 spi0: <Armada 37x0 SPI controller> mem 0x10600-0x10fff irq 6 on simplebus1 iichb0: <Marvell Armada 37x0 IIC controller> mem 0x11000-0x11023 irq 7 on simplebus1 iicbus0: <OFW I2C bus> on iichb0 iic0: <I2C generic I/O> on iicbus0 iichb1: <Marvell Armada 37x0 IIC controller> mem 0x11080-0x110a3 irq 8 on simplebus1 iicbus1: <OFW I2C bus> on iichb1 iic1: <I2C generic I/O> on iicbus1 nxprtc0: <NXP PCF8563 RTC> at addr 0xa2 on iicbus1 gpio2: <ISSI IS31FL3199 9 channel light effect LED driver> at addr 0xce on iicbus1 gpiobus2: <OFW GPIO bus> on gpio2 gpioc2: <GPIO controller> on gpio2 uart0: <Marvell Armada 3700 UART> mem 0x12000-0x121ff irq 9,10,11 on simplebus1 uart0: console (115200,n,8,1) gpioc0: <GPIO controller> on gpio0 gpioc1: <GPIO controller> on gpio1 mvneta0: <NETA controller> mem 0x30000-0x33fff irq 14 on simplebus1 mvneta0: version is 10 miibus0: <MII bus> on gpiomdio0 mv88e151x0: <Marvell 88E1512 Gigabit PHY> PHY 1 on miibus0 mv88e151x0: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, 1000baseSX, 1000baseSX-FDX, auto mvneta0: Ethernet address: 00:e0:ed:b6:13:59 mvneta1: <NETA controller> mem 0x40000-0x43fff irq 15 on simplebus1 mvneta1: version is 10 mdio0: <MDIO> on mvneta1 mdioproxy0: <MII/MDIO proxy, MDIO side> on mdio0 e6000sw0: <Marvell 88E6141> on mdio0 e6000sw0: single-chip addressing mode e6000sw0: PHY at port 1 miibus1: <MII bus> on e6000sw0 e1000phy0: <Marvell 88E1000 Gigabit PHY> PHY 17 on miibus1 e1000phy0: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, auto e6000sw0: PHY at port 2 miibus2: <MII bus> on e6000sw0 e1000phy1: <Marvell 88E1000 Gigabit PHY> PHY 18 on miibus2 e1000phy1: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, auto e6000sw0: PHY at port 3 miibus3: <MII bus> on e6000sw0 e1000phy2: <Marvell 88E1000 Gigabit PHY> PHY 19 on miibus3 e1000phy2: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, auto e6000sw0: PHY at port 4 miibus4: <MII bus> on e6000sw0 e1000phy3: <Marvell 88E1000 Gigabit PHY> PHY 20 on miibus4 e1000phy3: none, 10baseT, 10baseT-FDX, 100baseTX, 100baseTX-FDX, 1000baseT, 1000baseT-master, 1000baseT-FDX, 1000baseT-FDX-master, auto e6000sw0: CPU port at 5 e6000sw0: fixed port at 5 e6000sw0: switch is ready. etherswitch0: <Switch controller> on e6000sw0 mvneta1: Ethernet address: 00:e0:ed:b6:13:5a xhci0: <Generic USB 3.0 controller> mem 0x58000-0x5bfff irq 16 on simplebus1 xhci0: 32 bytes context size, 32-bit DMA usbus0 on xhci0 ehci0: <Marvell Integrated USB 2.0 controller> mem 0x5e000-0x5ffff irq 17 on simplebus1 usbus1: EHCI version 1.0 usbus1 on ehci0 sdhci_xenon0: <Armada Xenon SDHCI controller> mem 0xd8000-0xd82ff,0x17808-0x1780b irq 25 on simplebus1 mmc0: <MMC/SD bus> on sdhci_xenon0 ahci0: <AHCI SATA controller> mem 0xe0000-0xe1fff irq 26 on simplebus1 ahci0: AHCI v1.30 with 1 6Gbps ports, Port Multiplier supported with FBS ahcich0: <AHCI channel> at channel 0 on ahci0 pcib0: <Marvell Armada 3700 PCIe Bus Controller> mem 0xd0070000-0xd008ffff irq 5 on simplebus0 pcib0: link up pci0: <OFW PCI bus> on pcib0 ath0: <Atheros 9280> at device 0.0 on pci0 [ath] enabling AN_TOP2_FIXUP ath0: [HT] enabling HT modes ath0: [HT] 1 stream STBC receive enabled ath0: [HT] 1 stream STBC transmit enabled ath0: [HT] 2 RX streams; 2 TX streams ath0: AR9280 mac 128.2 RF5133 phy 13.0 ath0: 2GHz radio: 0x0000; 5GHz radio: 0x00c0 armv8crypto0: <AES-CBC,AES-XTS,AES-GCM> Timecounters tick every 1.000 msec mvneta1: link state changed to UP ZFS filesystem version: 5 ZFS storage pool version: features support (5000) usbus0: 5.0Gbps Super Speed USB v3.0 usbus1: 480Mbps High Speed USB v2.0 spibus0: <OFW SPI bus> on spi0 mx25l0: <M25Pxx Flash Family> at cs 0 mode 0 on spibus0 mx25l0: device type w25q32, size 4096K in 64 sectors of 64K, erase size 4K nxprtc0: registered as a time-of-day clock, resolution 0.015625s ugen1.1: <Marvell EHCI root HUB> at usbus1 uhub0 on usbus1 uhub0: <Marvell EHCI root HUB, class 9/0, rev 2.00/1.00, addr 1> on usbus1 ugen0.1: <Generic XHCI root HUB> at usbus0 uhub1 on usbus0 uhub1: <Generic XHCI root HUB, class 9/0, rev 3.00/1.00, addr 1> on usbus0 mmc0: Failed to set VCCQ for card at relative address 2 mmcsd0: 8GB <MMCHC DG4008 0.1 SN A401600F MFG 09/2019 by 69 0x0000> at mmc0 50.0MHz/8bit/65535-block mmcsd0boot0: 4MB partition 1 at mmcsd0 mmcsd0boot1: 4MB partition 2 at mmcsd0 mmcsd0rpmb: 4MB partition 3 at mmcsd0 CPU 0: ARM Cortex-A53 r0p4 affinity: 0 Cache Type = <64 byte D-cacheline,64 byte I-cacheline,VIPT ICache,64 byte ERG,64 byte CWG> Instruction Set Attributes 0 = <CRC32,SHA2,SHA1,AES+PMULL> Instruction Set Attributes 1 = <> Instruction Set Attributes 2 = <> Processor Features 0 = <GIC,AdvSIMD,FP,EL3 32,EL2 32,EL1 32,EL0 32> Processor Features 1 = <> Memory Model Features 0 = <TGran4,TGran64,SNSMem,BigEnd,16bit ASID,1TB PA> Memory Model Features 1 = <8bit VMID> Memory Model Features 2 = <32bit CCIDX,48bit VA> Debug Features 0 = <DoubleLock,2 CTX BKPTs,4 Watchpoints,6 Breakpoints,PMUv3,Debugv8> Debug Features 1 = <> Auxiliary Features 0 = <> Auxiliary Features 1 = <> AArch32 Instruction Set Attributes 5 = <CRC32,SHA2,SHA1,AES+VMULL,SEVL> AArch32 Media and VFP Features 0 = <FPRound,FPSqrt,FPDivide,DP VFPv3+v4,SP VFPv3+v4,AdvSIMD> AArch32 Media and VFP Features 1 = <SIMDFMAC,FPHP DP Conv,SIMDHP SP Conv,SIMDSP,SIMDInt,SIMDLS,FPDNaN,FPFtZ> CPU 1: ARM Cortex-A53 r0p4 affinity: 1 Release APs...done TCP_ratelimit: Is now initialized e6000sw0port1: link state changed to DOWN Trying to mount root from zfs:pfSense/ROOT/default []... e6000sw0port2: link state changed to DOWN e6000sw0port3: link state changed to DOWN e6000sw0port4: link state changed to DOWN uhub1: 2 ports with 2 removable, self powered uhub0: 1 port with 1 removable, self powered ugen0.2: <Sierra Wireless, Incorporated EM7305> at usbus0 u3g0 on uhub1 u3g0: <Sierra Wireless, Incorporated EM7305, class 0/0, rev 2.00/0.06, addr 1> on usbus0 u3g0: Found 4 ports. Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Root mount waiting for: CAM Dual Console: Serial Primary, Video Secondary random: unblocking device. -

Wouldn't it show at the top like it use to??

-

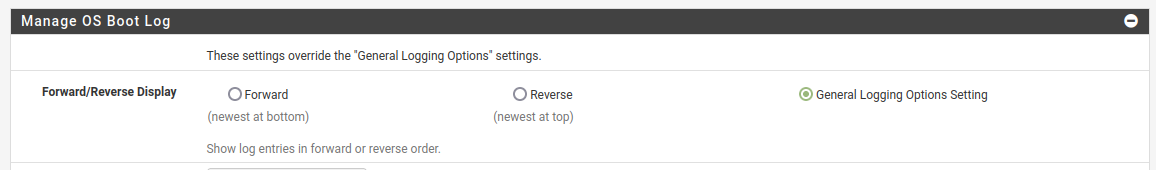

Yes, it does. It looks like you have the logs set as reversed though in 23.09.1, hence it's at the bottom of the page.

-

Weird I never changed that, is that a config.xml item?

-

Yes there's a general settings for in the log settings but you can also set it for each log.

-

Shouldn't the time stamps work for this log area? The GUI has columns for them.

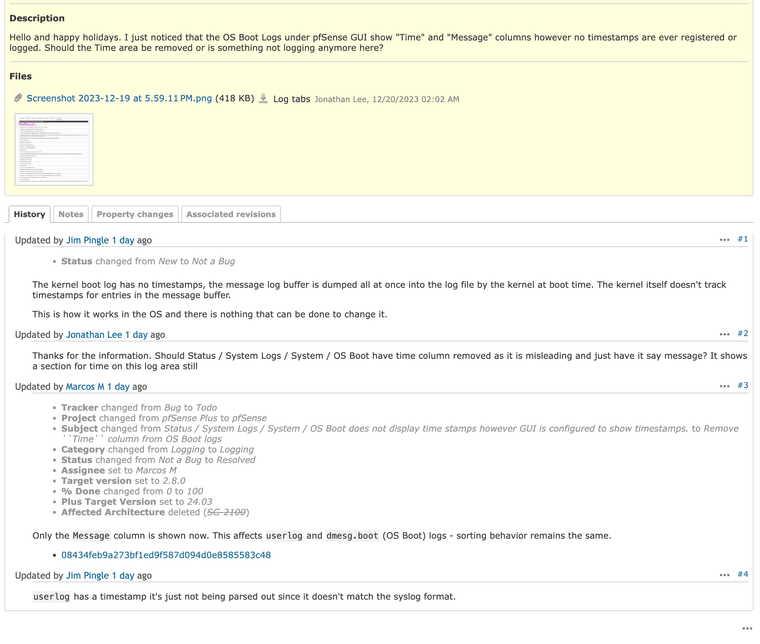

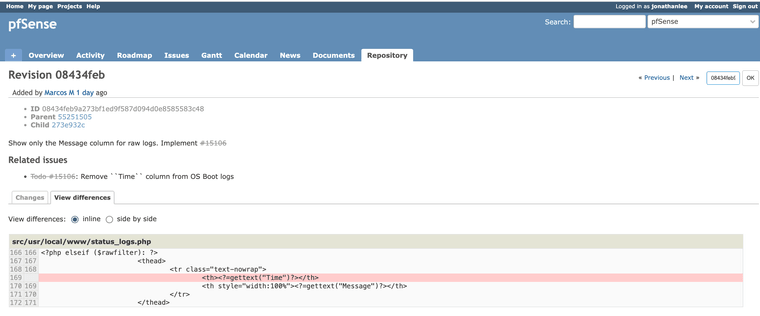

https://redmine.pfsense.org/issues/15106

-

No the message buffer boot logs (/var/log/dmesg.boot) doesn't have timestamps.

-

@stephenw10 Would you agree the GUI log area for OS boot has a typo then that causes some confusion.

It should only show Boot Log Entries on that.

-

Oh I see, yeah I guess. That's some work to display it differently than the other logs though for minimal gain.

-

Marcos fixed it !!

-

Nice!